# JETIR.ORG ISSN: 2349-5162 | ESTD Year : 2014 | Monthly Issue JOURNAL OF EMERGING TECHNOLOGIES AND INNOVATIVE RESEARCH (JETIR) An International Scholarly Open Access, Peer-reviewed, Refereed Journal

# LOW POWER PMOS BIASED SENSE AMPLIFIER

<sup>1</sup>P.Gopala Reddy, <sup>2</sup>K.Usha Maheshwari, <sup>3</sup>K.R.S.Gupta, <sup>4</sup>D.Durgasai, <sup>5</sup>K.Yasasri <sup>\*1</sup>Senior assistant professor, <sup>\*2, 3, 4,5</sup> Under Graduate Student

\*1Senior assistant professor, \*2, 3, 4,5 Under Graduate Student Department of Electronics and Communication Engineering Sri Vasavi Engineering College (Autonomous), Tadepalligudem, West Godavari, A. P

Abstract: The performance and environmental tolerance of CMOS memories are mostly determined by the sense amplifier in combination with memory cells. Sense amplifiers developed become a very big circuits-class due to their significant role in memory design. Two proposed PMOS biased sense amplifier circuits are presented in this paper. Regarding the recital, functionality, and dependability of the memory circuits, sense amplifiers are crucial. The suggested circuit is a PMOS biased sense amplifier that has a very high output impedance, less sense delay, less power dissipation, and performs the same functions as traditional circuits. Tanner EDA was used to simulate and evaluate the proposed sense amplifier's overall performance utilising 45nm library settings.

# Keywords: PMOS Sense Amplifier, Sense delay, Power Consumption.

## I. INTRODUCTION

Although microprocessors are used in computers, DSP, microprocessors, and microcontrollers, logic design memory are the most crucial component in digital system architecture. As a result, given all we are aware of, the system must take into account audio players with frequency and digital cameras with picture pixels. The data that is saved has higher quality, higher capacities, and shorter delays, which are needed for quick sensing. To improve the staging of towering, use sensing timings with continuous difference voltage and minimally used decoders and sense amplifiers. Hence, the circuit enrichment is made possible by the differential voltage, which appropriately depicts the amplifying signal. As a result, the SRAM cell, which has a faster but limited time. The identified memory chip that is used the majority of the time is in the sense amplifier memory. Consequently, the memory chip is crucial to the sense amplifier. So, it is clear from this article that bit lines are required for circuit changes involving memory data stored in amplified signals. We are all aware that the realm of advanced CMOS technology is mostly focused on system designers who want to create quick, low-power devices with sense amplifiers. The main quality of power, which affects signal delays in memory bit lines, has recently become more crucial. The problem arises as a result of the voltage signal replacing the current signal, and is solved by the replacement in the previous approach. The power of technology is afterwards decreased by the slight voltage variations in the circuit.

For better quality of saved data, low sensing delay and enhanced higher capacities are needed. Sense amplifiers are typically used to amplify the extremely small voltage differential on the bit lines at consistent sense timings in order to achieve the towering rate of staging. The SA is unable to correctly amplify the minute voltage difference if the sense amplifiers enable signal is asserted too early. If the SAE is claimed to be late, the overhead of access time and power consumption increases. Accordingly, for a high-speed and low-power SRAM cell, the ideal SAE timing is crucial. An amplifier for senses in recollections is one of the most important components. The sensory amplifier primarily recognises memory access times. Signals are amplified and deliver the data from the stored memory if any changes in the bit-lines are detected. Any creator will find it difficult to create a quick, low-power sense amplifier, especially in the context of submicron CMOS technologies. In terms of capacitance, additional signal delays today are primarily caused by memory bit lines. By sensing the current signal instead of voltage signals when the channel length is short, all these issues are reduced and eventually eliminated by the signal voltage gain. The current sensing method is the best option for low voltage, fast speed, and large memories. Why? Because there won't be a significant voltage fluctuation on the necessary bit-lines.

On the basis of operation modes, a sense amplifier may be classified as:

1.Voltage Sense Amplifier.

2. Current Sense Amplifier.

3. Charge Transfer Sense Amplifier (CTSA).

The differential pair is the most basic voltage sense amplifier. A small voltage swing that occurs on the bit line during cell reading is amplified by a differential couple and used to operate digital logic. The voltage sense amplifier, however, becomes useless as the bit line voltage swing decreases and approaches the same size as bit line noise. Because of their low input impedances, current mode sense amplifiers are primarily used in sense circuits. Small input and output impedances are advantageous because they reduce substrate modulations, voltage fluctuations, crosstalk, and sense circuit delays. voltage and currents on the base The very high bit line capacitance and the low output capacitance of the sense amplifier serve as the foundation for the CTSA's function. The increased bit-line capacitance is utilised by a differential charge transfer amplifier, which also provides a low-power function without compromising speed.

# II. LITERATURE SURVEY

For the cell, CMOS technology sense amplifiers were built, simulation results were delivered almost the worst-case scenario, progress and heat, sensing time below different power voltages V&, and busline capacitance values. As a result, it has been demonstrated that a memory sense amplifier's sensing latency is entirely reduced dynamically and its area as well, that its output are isolated from the busline or isolated from the dataline, depending on the situation, capacitances. The differential latch and clamped bit-line types of sense amplifiers are capable of this. We all understand that those sense amplifiers provide good sense time compared to the other research participants. Because of their resistance to reassuring process and operational temperature changes, two sense amplifiers are characterised in this way. establishing an electronic link between the sense using circuits and the busline prevents this from being more sensitive to the busline capacitances.

#### **III. METHODOLOGY**

3.1

The sense amplifier is the chip's memory in the circuit, according to the methods mentioned above, making it the most crucial component. The sensing amplifier in the circuit can be used to identify a completely capable device that can access time while being at ease in memory. Nonetheless, from any conversion in the entire bus-lines identified, which can obtain with the full signals are amplified with the equivalent of the developers' and suppliers' time and supplies within the boost memory data. When the sense amplifier has minimal power in the field of significant CMOS technologies, the developer should create the quick output.

So, in recent times, the memory bus lines can be mostly blamed for the additional signal latency that results from the signal's earlier capacitance and reliance. Signal sensing experiences complete problems when the length of the demodulating channel is low and the signal voltage gain diminishes. With all the voltage signals in the circuit being overridden. The sensing of current from the amplifier will be a preferable strategy in this situation because of the low voltage, increased speed, and larger memory. So, we are aware that there is no voltage.

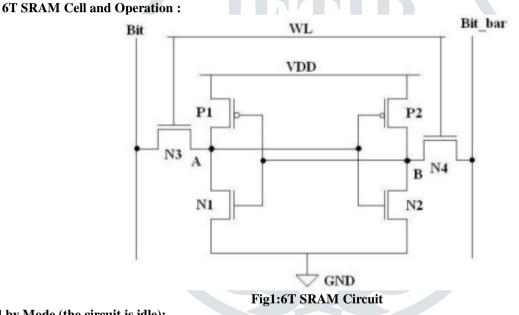

#### *a*) Stand by Mode (the circuit is idle):

The pass transistors N3 and N4 that link the bit lines to the 6t cell are turned off because the word line is not asserted in standby mode (word line=0). It indicates that the phone is not reachable. The latch will retain the data as long as the two cross-coupled inverters N1 and N2 are connected to the supply and continuing to feed back on each other.

#### b)Read Mode (the data has been requested):

The access transistor that will link the cell to the bit lines is enabled when the word line is affirmed in read mode (word line=1). Node a and node b's data are now transmitted to the bit lines. Assuming that 1 is kept at node A, the bit line will discharge through the driver transistor (N1) and be drawn up through the load transistors (P1) towards VDD. Read reliability is required when designing an SRAM cell (reading data without causing any disruptions).

#### c).Write Mode (updating the contents):

Think about the scenario where we want to enter a 0 into a space that was meant to contain a 1. Raising the word line to VDD and lowering the bit line to 0V and bit bar to VDD will pick the cell. Since each inverter is built to meet PMOS and NMOS, the inverter threshold is frequently fixed at VDD/2. If we want to put 0 at node a, N3 operates in saturation. At first, the supply voltage is 1. Due to the fact that N3 is a more powerful access transistor than N1, it pulls N2's drain terminal, which is originally at 1, down. A new value has been written, causing the bit line to be lowered to 0V and the bit bar to VDD as a result of P1 and N2 being turned on. The lowest bit line voltage required to alter a cell's state is what is meant by the requirement that SRAM be able to write.

## **3.2 PMOS BIASED TYPE SENSE AMPLIFIERS:**

# a) Sense Amplifier Circuit-1:

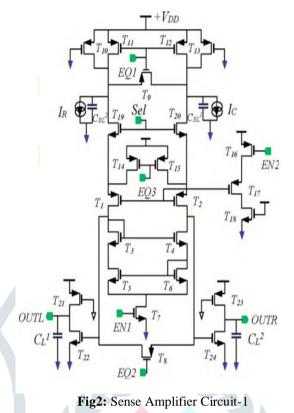

The sense amplifiers process is divided into two steps: detecting the signal before charging it, and sensing the signal after it has been amplified by the circuit. From the beginning of the charging period to each signal that needs to be stressed to finish sensing quantities of equal dimensions of specific voltages, the signal is applied. We can perform detecting at the same time as comparing the edges of the current signal amplifier. As a consequence of this replication, it is validated by the observation of the improved memory cell in the entire circuit. The sense amplifier circuit-1 in the image below displays resistance with a high output and no static error. circuit contains transistor T1 gate terminals, T2 and T7 short-connected transistor terminals. The transistors T1, T2, and T7 gate contacts are all shorted

#### © 2023 JETIR March 2023, Volume 10, Issue 3

#### www.jetir.org (ISSN-2349-5162)

together in the circuit shown in the below figure. As output resistance rises, Ir diverges more from Ic. Ir will pass through bus line BL1, and IL2 will pass by bus line BL2. T3-T4 and T5-T6 transistor pairs precisely match. Since the input and output potentials are roughly equal, the input and output currents are also equal in theory. Comparing the new type of sense amplifiers to the old type, fewer transistors are used.

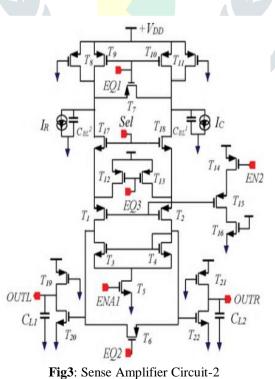

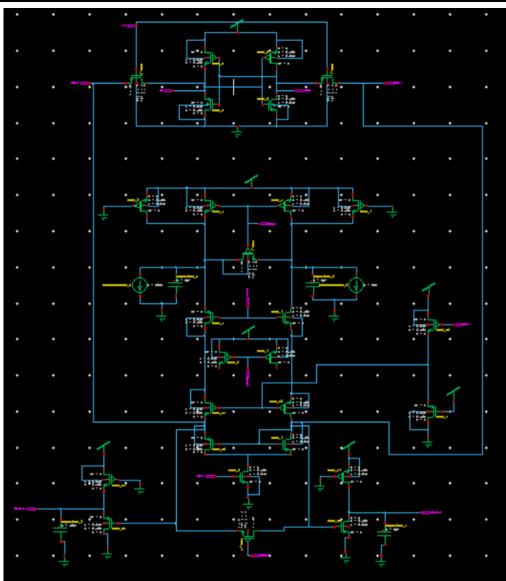

#### b) Sense Amplifier Circuit-2:

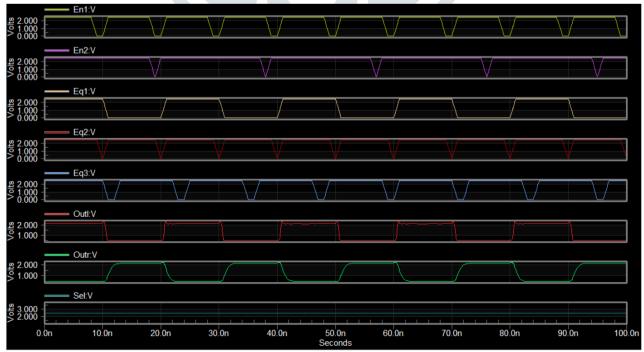

The transistors T7 to T11 are located in the section of the circuit that charges the bit lines during the pre-charging amplifier phase. To supply the circuitry with the differential currents and voltage, the input is chosen carefully. Three equaliser inputs are used in this endeavour to bring the bit lines up to the system's equal potential. Furthermore, equalizer1 typically has the marking EQ1 on it. The outputs out L and out R are shared by the inverters that are linked in a circuit across the load capacitance. As a result, the voltage bias generator in the circuit supplies the gate signal for the third equalizer's EQ3 input. In terms of the circuit finding, there is only one base cell current mirror circuit present.

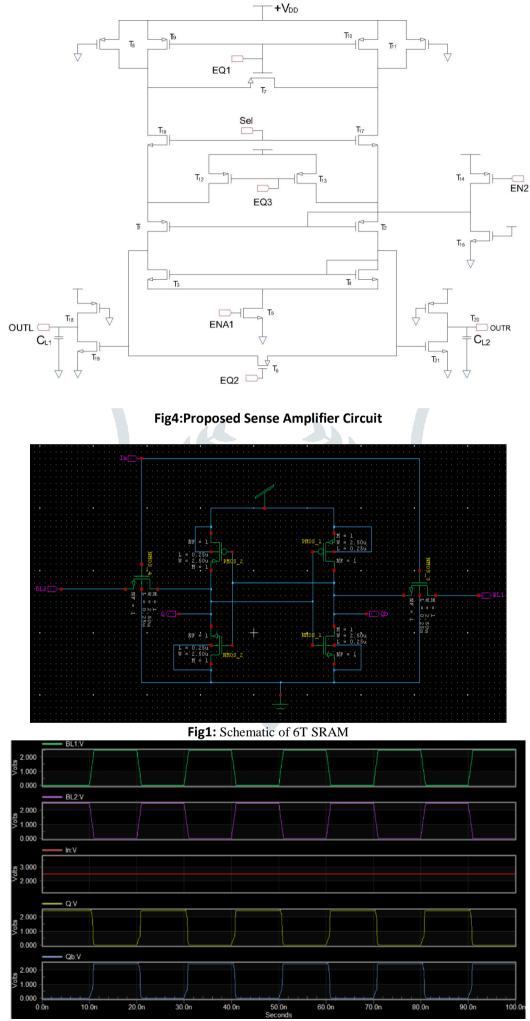

#### c).Proposed Sense Amplifier Circuit:

The sense amplifier consumes a lot of energy and makes use of numerous transistors. This is the recommended approach, where output OUTL is taken across transistors T2 and T4 and output OUTR is taken between transistors T1 and T3. As a result, we've established that removing transistor T15 reduces the circuit's power consumption and sense latency.

**IV. RESULTS :**

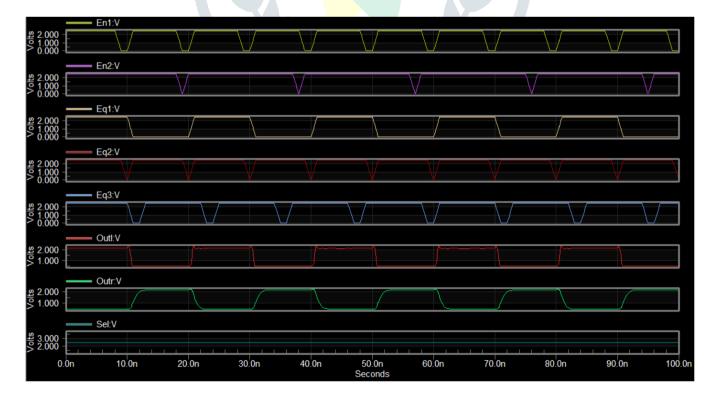

Fig2: Output waveforms of 6T SRAM

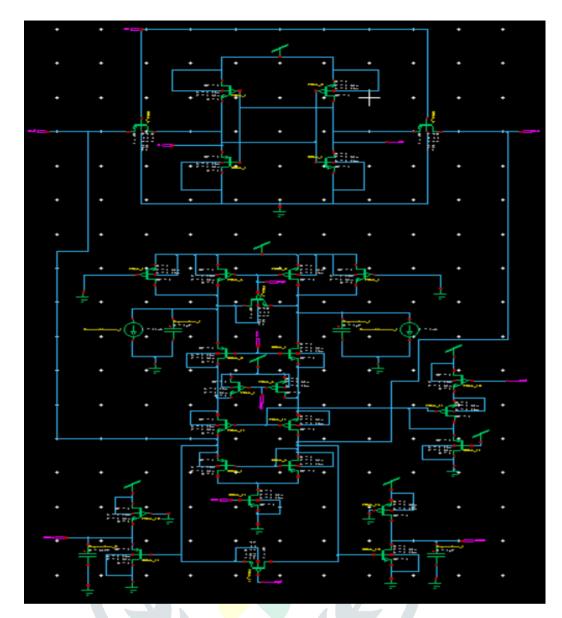

Fig.3: Schematic of sense amplifier circuit -2with SRAM

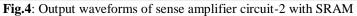

Fig.5: Schematic of proposed sense amplifier circuit with SRAM

Fig.6: Output waveforms of proposed sense amplifier circuit with SRAM

# © 2023 JETIR March 2023, Volume 10, Issue 3

# V. TABLES AND GRAPHS

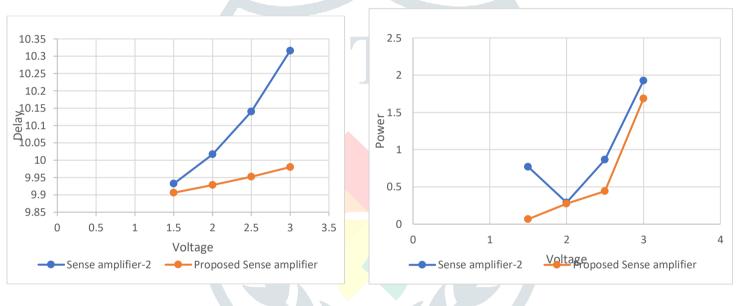

Table1: Voltage vs Delay

Graph1: Voltage vs Delay

| Voltage(v) | Delay(ns)         |                             |

|------------|-------------------|-----------------------------|

|            | Sense Amplifier-2 | Proposed Sense<br>Amplifier |

| 1.5        | 9.9319            | 9.9060                      |

| 2          | 10.0167           | 9.9280                      |

| 2.5        | 10.1401           | 9.9519                      |

| 3          | 10.3159           | 9.9801                      |

Table2: Voltage vs Power

| Voltage(v) | Power(watts)      |                             |

|------------|-------------------|-----------------------------|

|            | Sense Amplifier-2 | Proposed Sense<br>Amplifier |

| 1.5        | 0.7985            | 0.0671                      |

| 2          | 0.2905            | 0.2758                      |

| 2.5        | 0.8640            | 0.4419                      |

| 3          | 1.9273            | 1.6862                      |

# Graph2: Voltage vs Power

# VI. CONCLUSION

The proposed circuit have less number of transistors, so that sensing delay and power consumption are also reduced. This circuits are simulated in Tanner EDA tool with 45nm technology libraries. The simulated graphs is drawn for sense delay and power consumption at different supply voltages. Since power consumption plays crucial role in DSP application where SRAMs (sense amplifier is an essential part in SRAM) are widely used.

# **REFERENCES:**

[1] A. Chrisanthopoulos, Y. Moisiadis, Y. Tsiatouhas and A. Arapoyanni, "Comparative study of different current mode sense amplifiers in

submicron CMOS technology", IEE Proc.-Circuits Syst., Vol. 149, No. 3, June 2002, pp.154-158.

[2] S. Yang, W. Wang, N. Vijayakrishnan, and Y. Xie, "Low-leakage robust SRAM cell design for sub-100 nm technologies", in Proc. ASPDAC, 2005, pp.539-544

[3] Mahendranath. B and Avireni Srinivasulu, "Performance analysis of a new CMOS output buffer", in proc. of IEEE International Conference on Circuit, Power and Computing Technologies, Kumaracoil, India, Mar 21-22, 2013, pp. 752-755. Doi: 10.1109/ICCPCT.2013.6529041.

[4] Z.H. Kong, K.S. Yeo, and C.H. Chang, "An ultra low-power current mode sense amplifier for SRAM applications", J. Circuits, Syst. Compute, Vol. 14, No. 5, pp. 939-951, 2005.

[5] Yeo, K.S. Goh ,W.L. Kong, Z.H. Zhang, Q.X., and Yeo, W.G.: "High performance low-power current sense amplifier", IEE Proc., Circuits Devices Syst., Vol. 149, No. 56, pp.308-314, 2002

[6] K.S. Yeo, W.L. Goh, Z.H. Kong, Q.X. Zhang, W.G. Yeo, "High performance, low-power current sense amplifier using a cross coupled current-mirror configuration", IEEE Proc. Circuits Device Syst., Vol. 149, No. 56, pp. 308-314, Oct./Dec. 2002.

[7] E. Seevinck, P. J. Van Beers and Ontrop, "Current-mode techniques V for high-speed VLSI circuits with application to current sense amplifier for CMOS SRAMs", IEEE J. Solid-State Circuits, 1991, Vol. 26, No. 4 pp. 525-536.

JETIR2303701 Journal of Emerging Technologies and Innovative Research (JETIR) <u>www.jetir.org</u> h7

[8] K. Kanda, H. Sadaaki, and T. Sakurai, "90% Write power-saving SRAM using sense-amplifying memory cell", IEEE J. Solid-State Circuits, Vol. 39, pp. 927-933, June. 2004

[9] Blalock and Jaeger, "A high-speed clamped bi-line current-mode sense amplifier", IEEE J. Solid-State Circuits, 1991, Vol. 26, No. 4, pp. 542-548.

[10] M.H. Tu, J.Y. Lin, M.C. Tsai, S.J. Jou, and C.T. Chuang, "Single ended subthreshold SRAM with asymmetrical write/read-assist", IEEE Trans. Circuits Syst. I, Reg. Papers, Vol. 57, No. 12, pp.3039-3047, Dec.2010